Des crayons de couleur, du papier calque quadrillé, un rouleau de scotch : des étudiants conçoivent des circuits intégrés. Une première en Europe

Publié par Alain Guyot, le 8 avril 2021 2k

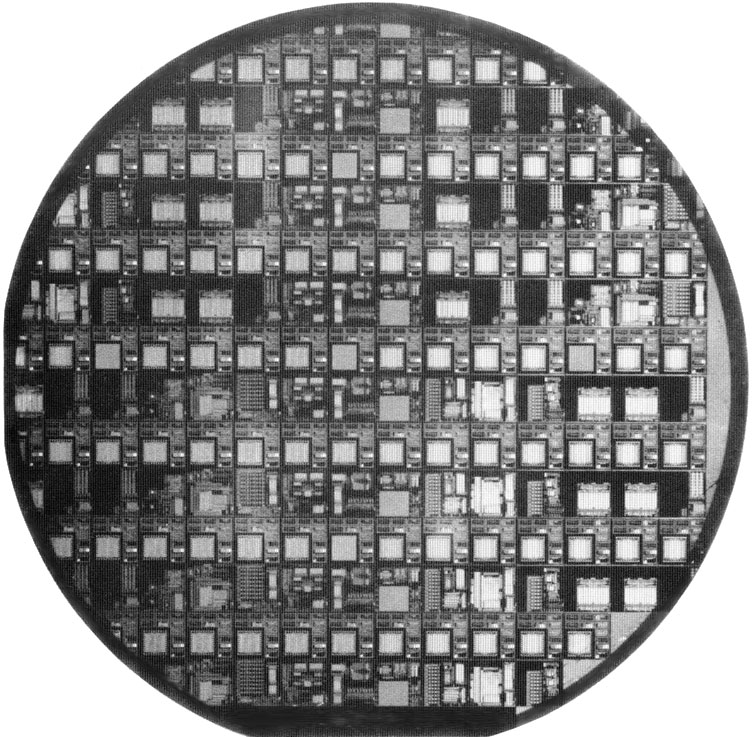

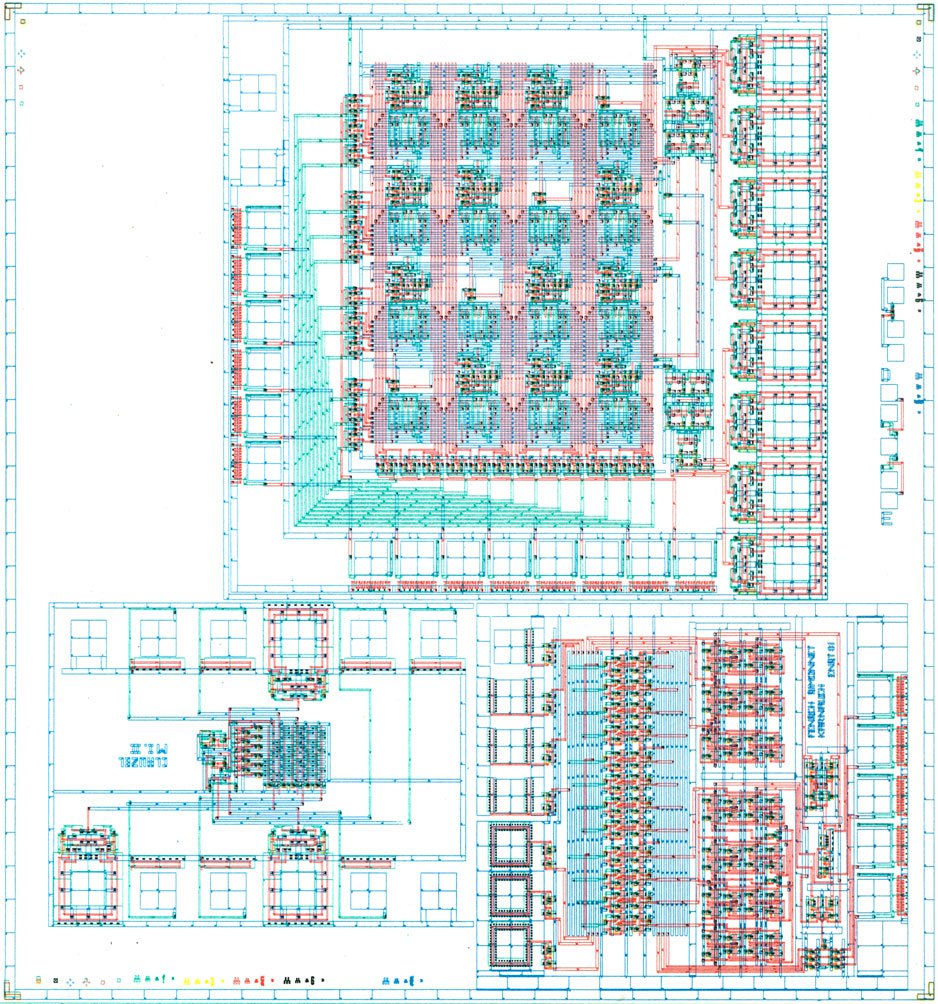

Tranche de silicium avec 48 circuits intégrés d’enseignement/recherche

par Alain Guyot, membre du bureau de l'ACONIT

(ex-responsable conception du DEA de Microélectronique de Grenoble)

Il y a 40 ans, en 1980-1981 démarrait en France un enseignement de conception de circuits intégrés numériques. Ces cours devaient être accompagnés de la conception par les étudiants, suivi de la fabrication, de circuits intégrés réels, quoique très simples au début.

Comme l’habilitation du DEA (Diplôme d'Études Approfondies, devenu Master 2 Recherche) de microélectronique, tout juste créé sous la responsabilité d’Alain Deneuville, excluait les travaux pratiques, les séances de conception ne furent pas inscrites comme des TP mais comme des « ateliers d’élaboration de circuits ».

Dans ce domaine on pensait avoir juste 18 mois de retard sur les américains, mais un article du professeur Lynn Conway paru en 2012 dans « IEEE Solid State Circuits Magazine », date les premiers circuits conçus par des étudiants à décembre 1978 au MIT (Boston). Nous avions donc moins de 2 ans et demi de retard.

Par contre nous pensions être les premiers en Europe, ce qui nous fut confirmé plus tard par la participation au projet européen « Eurochip » de formation en microélectronique. Le projet Esprit 3/Eurochip, administré par les Allemands, a coordonné les enseignements belges, danois, anglais et bien sûr français. On estime que 10 000 étudiants européens par an étaient concernés par cet enseignement dans les années 90.

Il faut l’avouer, il est un peu prétentieux de s’autoproclamer premier. Des nombreux circuits intégrés avaient déjà été conçus et fabriqués par des universités des deux côtés de l’atlantique. Mais il s’agissait de circuits de recherche, conçus par des doctorants et leur encadrant, et non par des étudiants. Nuance.

L’enseignement en conception de circuits intégrés à Grenoble ne partait pas de rien en 1980. Le laboratoire TIM3 avait acquis un peu d’expérience en collaborant avec les concepteurs de la société EFCIS, notamment Michel Henry, Michel Vergniault et Jean-Pierre Moreau, sur un microprocesseur en technologie avancée pour l’époque : CMOS (Complementary Metal Oxide Semiconductor) sur isolant (ancêtre lointain du SOI -Silicon on Insulator- de STmicroelectronics).

Enfin les professeurs Carver Mead du Caltech (Los Angeles) et Lynn Conway de Xerox Parc (Palo Alto) avaient entrepris de promouvoir la formation en conception de circuits intégrés dans les universités américaines. Notons en passant que le professeur Carver Mead est l’inventeur du terme « loi de Moore ».

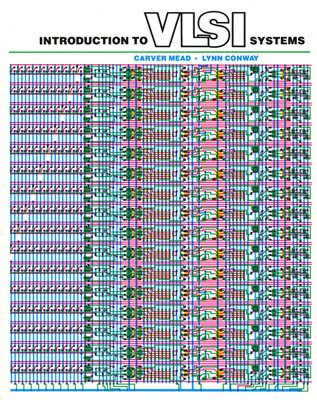

Mead et Conway avaient donc en 1978 édité un livre, « Introduction to VLSI systems » traduit en français en 1983, et surtout conçu un kit « Instructor’s Guide to VLSI System Design » pour la formation des formateurs, accompagné de « A Guidebook for the Instructor of VLSI System Design » . Mead et Conway nous ont reçu, nous ont dédicacé leur livre, et surtout confié ce copieux kit, traitant l’INPG (maintenant Grenoble‑INP) à l’égal d’une université américaine.

Le livre séminal de Mead et Conway qui a démythifié la conception

La seule chose à laquelle nous n’avons pas eu accès, c’est la fonderie de silicium MOSIS (MOS Implementation Service), qui était fermée aux universités non américaines. C’est ce déni d’accès aux fonderies de silicium américaines qui justifie cet article. Ce fut probablement une chance car le service CMP (Circuit Multi Projet) fut fondé pour pallier l’interdiction d’utiliser MOSIS. Les services de courtage en silicium MOSIS et CMP existent toujours en 2021, se portent bien et coopèrent mais, confidentiellement, le CMP est dorénavant aussi important que MOSIS.

Fabriquer un circuit intégré

Pour concevoir et fabriquer un circuit intégré il faut :

1 – une technologie

2 – des outils informatiques et un langage de description de circuit

3 – une bibliothèque de blocs fonctionnels pré-dessinés et pré-caractérisés

4 – un fabriquant de masques de photolithographie (réticules)

5 – un fondeur de silicium.

La technologie

Dans le cadre présent, ce terme désigne l’ensemble des règles électriques et topologiques que le concepteur doit impérativement respecter pour que le circuit (les transistors MOS) fonctionne.

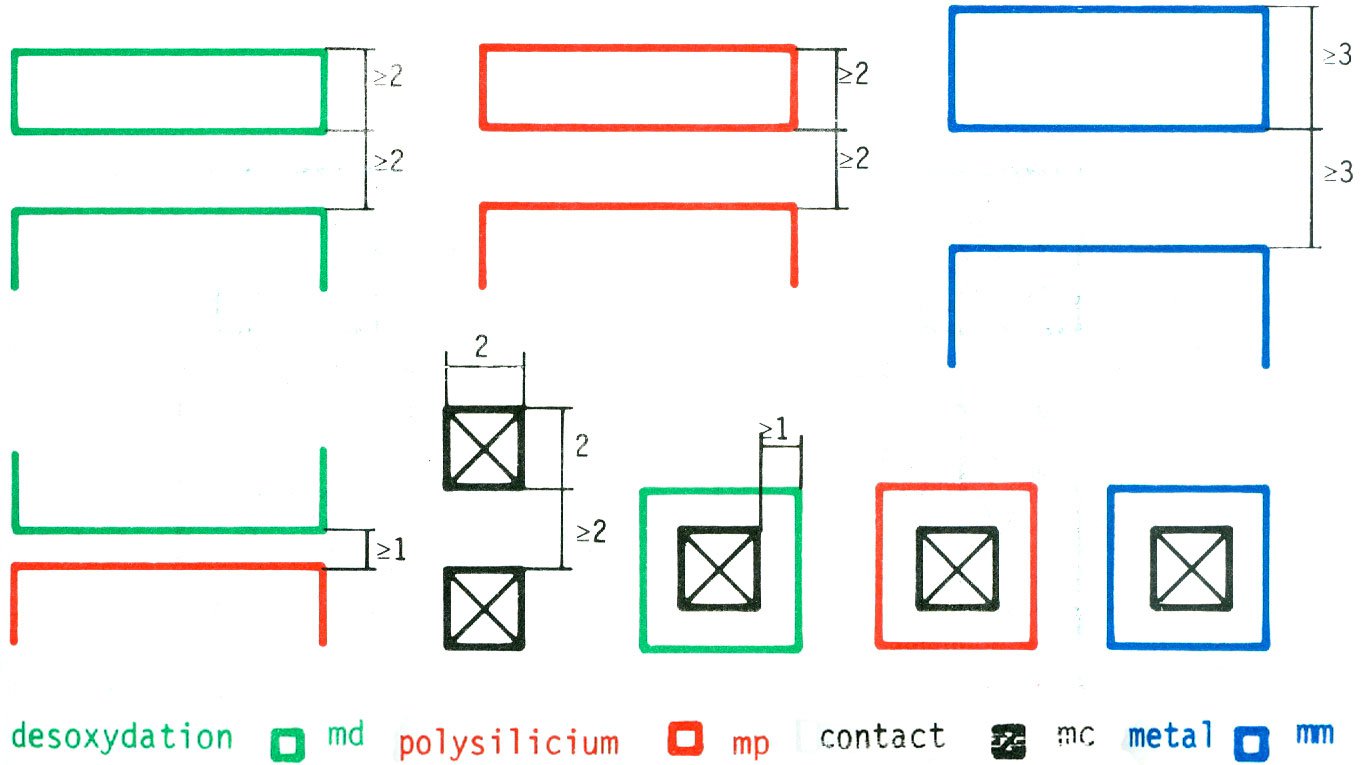

Notre technologie a 3 niveaux de conducteurs superposés et séparés par de l’isolant (du SIO2, autrement dit du verre) : la désoxydation, dessinée en vert, le polysilicium (silicium polycristallin), dessiné en rouge et le métal (aluminium), dessiné en bleu. Ces noms barbares dérivent de la façon de les obtenir par des procédés chimiques et thermiques.

Ci-dessous les règles de dessin très simplifiées tirées du Mead&Conway. Le « contact », dessiné en noir, est une ouverture dans l’isolant pour connecter électriquement le conducteur de dessous avec celui de dessus à travers l’ouverture. La technologie est « autoalignée », quand un conducteur vert croise un conducteur rouge, on obtient un transistor MOS. Grossièrement, parce que l’oxyde qui sépare ces deux couches est très mince, le champ électrique du polysilicium (rouge) change la conductivité du semi-conducteur (vert) qu’il croise.

Règles simplifiées de dessin de circuit. Les chiffres sont des dimensions virtuelles

La fabrication du jeu de masques

Un masque est une plaque de verre sur laquelle on a dessiné un des niveaux du circuit intégré (md, mp, mc ou mm). Il y a donc un masque par niveau plus quelques niveaux déduits des précédents par informatique. Le dessin du masque doit être extrêmement précis et absolument sans flou. La fabrication des masques est un métier, pour lequel la société NanoMask a été fondée en 1983 au Rousset, près d’Aix-en-Provence (fermée en 2003).

Le langage de description

Le langage LUCIE (Langage Universitaire des Circuits Intégrés pour l’Enseignement), défini par François Anceau en 1980 est un « langage à balises » qui décrit :

Des rectangles : REC(x, y, dx, dy, nn). "nn" est le niveau: md, mp, mc ou mm

Des opérateurs topologiques : translation, symétrie, rotation, répétitions

Des figures, qui sont des collections de rectangles, d’opérateurs ou de figures. De ce point de vue, un circuit fini et une figure.

On a assez rapidement ajouté des polygones. C’était une surcouche purement cosmétique. Un logiciel fusionnait les rectangles adjacents pour afficher un polygone, ou au contraire décomposait un polygone saisi en rectangles. Le plot de sortie du paragraphe suivant est dessiné en polygone alors que plus loin le circuit fini est dessiné en rectangles.

Les outils informatiques

Le numériseur : les étudiants dessinaient au crayon de couleur une partie de leur projet (une figure) sur une feuille de papier quadrillé. Cette feuille était ensuite scotchée sur une tablette graphique, puis on pointait les coins opposés de tous les rectangles un par un, après avoir sélectionné un niveau. Le dessin apparaissait progressivement sur l’écran d’un terminal graphique Tektronix 4014, en noir de blanc, bien sûr.

L’éditeur graphique : l’écran de la TK4014 était alors divisé : à droite le texte Lucie, et à gauche le dessin correspondant. Le dispositif de pointage de la TK4114 (2 molettes crantées déplaçant un réticule sur l’écran) pointait un rectangle dans le dessin, auquel le logiciel faisait correspondre une ligne du texte Lucie. On pouvait alors modifier au clavier les paramètres (position, taille) de ce rectangle dans le texte Lucie.

La TK4014 avait une excellente résolution : 4000x4000 pixels, mais ne permettait pas d’effacer individuellement un objet sur l’écran. Toute modification était un effacement total suivi d’un ré-affichage de la figure modifiée. C’était lent.

Le numériseur et l’éditeur graphique ont été écrits en Fortran par un ingénieur stagiaire plein d’avenir : Ahmed Amine Jerraya.

La bibliothèque

La bibliothèque était riche (ou pauvre, c’est selon) de seulement neuf figures, des plots d’entrée ou de sortie provenant du Mead&Conway et numérisés en LUCIE.

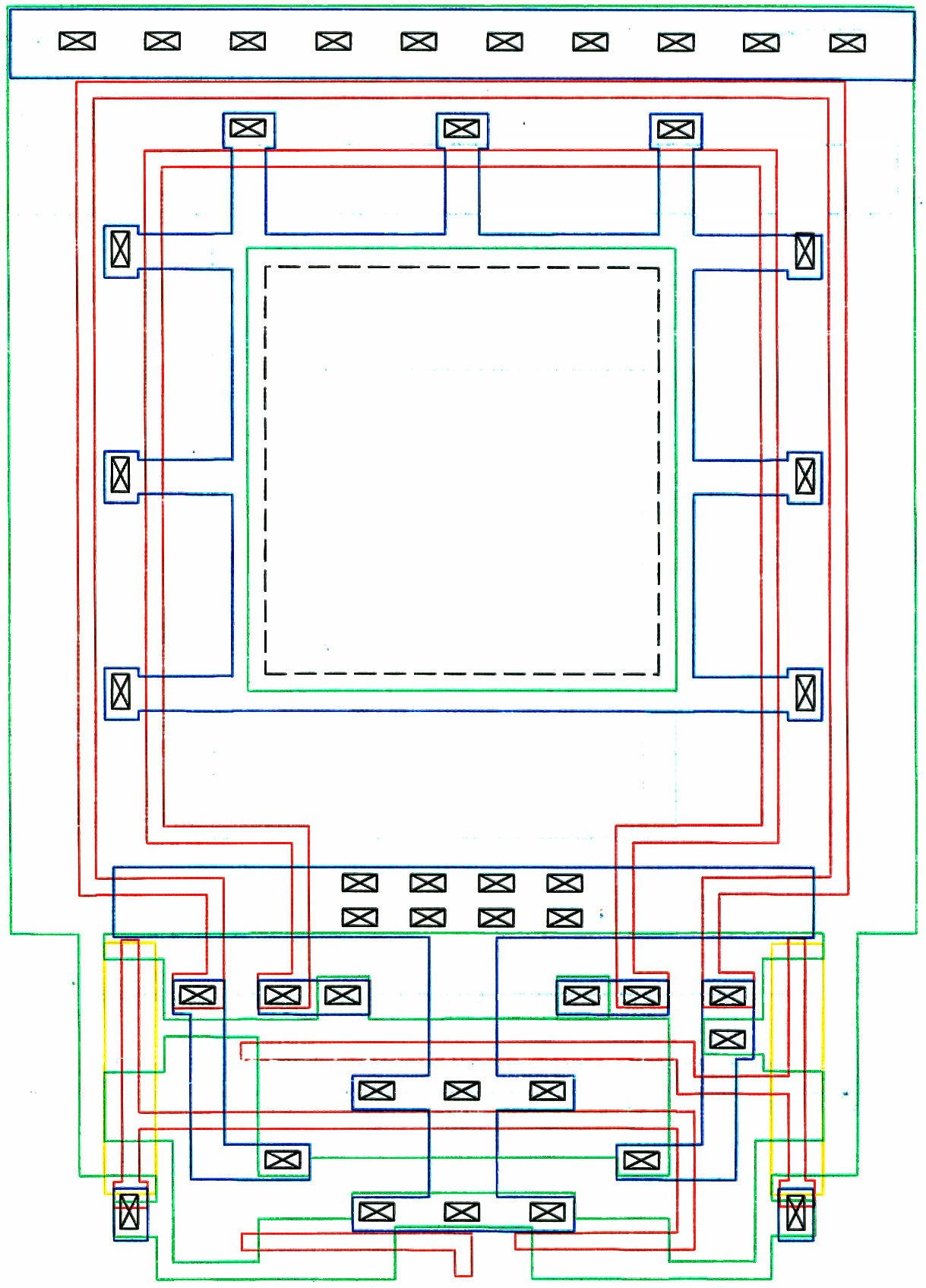

Ci-dessous un plot de sortie, qui permet au circuit intégré de communiquer électriquement avec le monde extérieur. Le carré pointillé au centre est une ouverture dans la passivation (la couche d’émail qui enrobe le circuit fini pour le protéger de la pollution). A travers cette ouverture on soudera sur le métal du circuit intégré (en bleu), par une combinaison de pression et d’ultrasons, un fil d’aluminium dont l’autre extrémité sera soudée au boîtier du circuit.

Dessin d’un plot de sortie vers l’extérieur du circuit

La fabrication du jeu de masques

Un masque est une plaque de verre sur laquelle on a dessiné en noir un des niveaux du circuit intégré (md, mp, mc ou mm). Il y a donc un masque par niveau plus quelques niveaux déduits des précédents par informatique. Le dessin du masque doit être extrêmement précis et absolument sans flou. La fabrication des masques est un métier, pour lequel la société NanoMask a été fondée en 1983 au Rousset, près d’Aix-en-Provence (fermée en 2003).

La Gyrex de l’Université de Louvain-la-Neuve

La machine Gyrex est une photocomposeuse qui dessine des rectangles pleins (pas seulement le contour) sur une plaque photographique. Elle comporte une lampe à décharge, un diaphragme rectangulaire ajustable mécaniquement, un objectif et une table photographique mobile. Pour dessiner un rectangle REC (x, y, dx, dy) on ajuste les dimensions du diaphragme à (dx, dy) avec des moteurs pas à pas puis on déplace pas à pas la table qui supporte la plaque photographique en (x, y) et enfin on insole avec la lampe flash.

L’image rectangulaire du diaphragme est alors projetée optiquement sur la plaque photographique. Puis on passe au rectangle suivant. Après développement, la plaque photographique est transférée par photocontact sur une plaque de verre.

On procède ainsi pour chacun des niveaux de la technologie et on obtient un jeu de masques pour fabriquer le circuit intégré.

La Gyrex lit ses commandes sur un ruban de papier perforée . La photo montre la Gyrex en salle blanche et chambre noire et en bas le lecteur de ruban de papier. L’opérateur est vraisemblablement Maurice Lobet, du laboratoire de microélectronique de l’université de Louvain.

La Gyrex avait cependant quelques défauts : 1 – les dimensions maximales du diaphragme limitent la taille des rectangles. Il faut donc découper les rectangles trop grands en plusieurs rectangles plus petits adjacents. 2 – le jeu de la mécanique. Lorsqu’un rectangle est découpé en deux rectangles plus petits adjacents, il se peut que leurs dessins sur la plaque photographique s’aboutent mal à cause du jeu dans le déplacement de la table. Il y a alors entre les deux rectangles dessinés de petits défauts visibles seulement au microscope. Pour pallier la limitation dûe à la précision, l’un des rectangles est légèrement étendu de façon à recouvrir légèrement l’autre. 3 – la Gyrex, électromécanique, est désespérément lente. Aussi un traitement logiciel préalable essaye de minimiser le nombre de commandes sur le ruban perforé, en dessinant préférentiellement des rectangles tous de mêmes dimensions, et de minimiser les distances de déplacement de la plaque photographique en triant les rectangles. 4 – le transfert de Grenoble vers Louvain-la-Neuve consistait à expédier par la poste une boîte contenant les rubans perforés, dûment marqués au feutre sur l’amorce. L’utilisation du réseau ARPANET qui reliait dès 1980 les grandes universités américaines développant leur enseignement de conception VLSI était à l’époque un avantage considérable pour rassembler les projets en Amérique.

Portion d’un masque en verre 10x produit par la Gyrex.

Niveau Métal (bleu) du circuit ci-dessous

Examinez la figure ci-dessous : elle n’est pas issue d’une table traçante couleur (acquise en 1982) mais d’une impression offset 5 couleurs grâce aux soins de M. Iglesias, responsable du service reprographie de l’IMAG.

Les rectangles ont été découpés pour la Gyrex, un point marque le côté étendu pour le recouvrement. Le jeu de masques « 10x » de ce circuit dessinés par la Gyrex est conservé à ACONIT. Lors de l’élaboration du circuit intégré par photolithographie, les images des masques « 10x » sont réduits optiquement à un dixième.

Il y a dans ce circuit intégré CMP (Circuit Multi Projet) 3 projets d’étudiants (DEA et Ingénieur). Au montage en boîtier, seul l’un de ces trois circuits intégrés sera connecté au boîtier, les autres sont perdus. Ce premier CMP était un coup d’essai. La même année un second circuit intégré CMP regroupera 5 projets, portant à 8 le total de 1981.

Et après ?

En 1981-1982, 27 projets. Masques fabriqués par Micromask, Californie, USA, après conversion de LUCIE en GDS II par l’ordinateur CALMA du CNET (logiciel LuCa de Bernard Conq). Technologie du CNET à Meylan (devenu Orange Labs), grâce à Patrice Senn et Jean‑Louis Lardy, soutenu par l’association G.C.I.S. (Groupement Circuit Intégré Silicium) qui regroupe le CNRS, le CEA-LETI et le CNET. Les projets en LUCIE sont encore expédiés à Grenoble par la poste sur une bande magnétique (ou bien en voiture pour les retardataires). Cette année-là l’ « École d’été du Forez » à Chalmazel (Loire) fut consacrée à la formation des formateurs en conception de circuits intégrés.

En 1982-1983, 48 projets (25 par des étudiants et 23 par des chercheurs). Masques fabriqués par Nanomask (Aix-en-Provence) et technologie du CNET à Meylan. Photo de la rondelle de silicium en tête de cet article.

A partir de 1984, LUCIE est progressivement abandonné car les universités se sont dotées de logiciels commerciaux : Cadence, Compass, Mentor (licences acquises par le CNFM avec une réduction de 90%) et de stations de travail Sun ou Microvax. Passage à une fonderie industrielle : MHS (Matra Harris Semiconductors). Le nombre de projets d’enseignement va culminer à 101 en 1993, puis décroitre jusqu’à 2 à 5 par an. En effet les logiciels de conception sont devenus si performants et fiables que le circuit intégré se comporte exactement comme son modèle simulé. Il n’est utile de fabriquer que les circuits qui seront réelement utilisés. Les autres sont virtuels.

Les transistors du CMP81 avaient une longueur de canal dessinée de 8 microns. Cette dimension a été depuis divisée en 40 ans par plus de 3 ordres de grandeur.

Bibliographie

Charles Trullemans : Histoires de mon laboratoire : Le laboratoire de microélectronique de l’UCL de 1958 à nos jours

François Anceau, Yvan Bonnassieux: Conception Des Circuits VLSI - Du Composant Au Système

Alain Guyot : Le CMP 81 (rapport d’activité GCIS)