Recherche, industrie, informatique : Elaboration du langage Cassandre, 1966-1975 (11/12 - année 2021)

Publié par ACONIT (Association pour un Conservatoire de l'Informatique et de la Télématique), le 22 octobre 2021 2.9k

Illustration d'en-tête : couverture de la thèse d'état de Docteur es-sciences mathématiques soutenue par Jean MERMET à l'Université Scientifique et Médicale de Grenoble en 1973 (détail)

CASSANDRE

Chronologie et intervenants (Juillet 1966 – Septembre 1975)

Synthèse par Xavier HIRON (ACONIT), à partir d'un témoignage de Jean MERMET,

ancien directeur de recherches au CNRS. Business angel.

Cassandre est un Langage de Transferts entre Registres (RTL) dont la conception et la réalisation nécessitèrent des recherches approfondies, menées au sein de l’IMAG, laboratoire auquel Jean Mermet était, à l’époque, rattaché en tant que jeune ingénieur en informatique. Celui-ci témoigne, dans un article posté sur le site de l’ACONIT (*voir la version complète), des tenants et aboutissants de cette aventure qui dura environs dix ans

En Juillet 1966, Jean Mermet, jeune étudiant-chercheur en informatique, sort de l’ENSIMAG. Il connait et fréquente l’équipe du Pr. Jean Kuntzmann et avait déjà à son actif quelques publications. Ce dernier le présenta à M. Sokoloff, de la compagnie Thomson, au sujet d’une formule écrite en APL (A Programming Language), langage inventé par Kenneth Iverson (IBM). M. Sokoloff, séduit par la description formelle du système 360 en APL, souhaitait lancer une coopération avec le laboratoire IMAG pour la compilation d’un système digital.

Cette coopération prit la forme d’un contrat de la DGRST. Elle fut d’autant plus efficace que l’interlocuteur chez Thomson (branche Française CFTH-HB) était F. Lustman, jeune docteur ingénieur à l’IMAG. Elle commença par un examen critique d’APL, suivi d’une large étude bibliographique. Ce travail jeta les bases de CASSANDRE, langage synthétisant l’état de l’art en 1966-67, et de ses deux compilateurs : l’un destiné à produire un programme de simulation du système logique décrit dans ce langage, l‘autre conçu pour générer les circuits matérialisant ce système.

Bientôt se joindront à l’aventure F. Anceau, qui développa un simulateur CASSANDRE codé en langage assembleur 360, et P. Liddell, qui produisit une thèse de 3ième cycle sur la compilation en schémas logiques de CASSANDRE.

I- CASSANDRE, un langage RTL

En 1966, aucun langage HDL (Hardware Description Language) n’était commercialisé. L’industrie de l’EDA (Electronic Design Automation) n’allait surgir qu'au début des années 1980, avec la création, sur la côte ouest des USA, des sociétés MENTOR Graphics, DAISY Systems et VALID Logic. La conception assistée par ordinateur (CAO) des circuits consistait essentiellement à utiliser des formalismes graphiques aidant les concepteurs à placer et interconnecter sur les cartes de circuits imprimés les boitiers de composants de la technologie de l’époque, ainsi que des programmes de vérification des connections et d’optimisation du nombre de couches planaires. Les outils utilisés étaient des stations de travail graphiques (Computer Vision ou Calma) équipées de programmes adaptés au marché des circuits imprimés. De petites compagnies constituèrent leurs catalogues de composants. Certaines offrirent un modèle exécutable, sorte de simulateur qui permettait de vérifier le fonctionnement et les performances attendus à partir d’un prototype virtuel.

Il existait dès le milieu des années 1960, chez les fabricants comme IBM, Burroughs, DEC et CAE en France, des études ayant débouché sur l’emploi de langages de nature fonctionnelle et se plaçant à un haut niveau d’abstraction. Pour stocker l’information, les primitives utilisées n’étaient plus des variables simples mais des variables de type tableaux et des fonctions de complexité arbitraire, appelées registres.

Le fonctionnement de l’ensemble était synchronisé par une ou plusieurs horloges. Le postulat était que tout transfert d’un élément de type registre à un autre, quel que soit le nombre de couches des circuits combinatoires les séparant, pouvait s’effectuer entre deux impulsions d’horloges. Les langages offrant ce type de spécifications s’appelèrent RTL : Register Transfer Languages, ou langages de transferts entre registres. CASSANDRE (Conception Assistée et Simulation des Systèmes logiques, leur ANalyse, Description et REalisation) appartient à cette catégorie.

L’adoption des RTL par l’industrie fut longue, car elle allait changer la méthodologie de conception : de bottom up (du structurel au fonctionnel) à top down (du fonctionnel à une implantation par un compilateur de circuits logiques (hardware compiler)). S’agissant du seul moyen d’accompagner la croissance explosive de la complexité des circuits (voir ci-dessous), ce type d’outil fut l’un des objets de nos travaux avec CASSANDRE.

(En 1966, Moore n’avait pas encore énoncé sa loi empirique sur la croissance de la complexité des circuits (boutade restée vraie durant 50 ans). Mais on pouvait pressentir la complexité exponentielle des modèles associés : un circuit dont le nombre de transistors double tous les 18 mois pendant 50 ans en contient 2**33 ; une unité contenant une hiérarchie à 10 niveaux, chacun contenant aussi 10 unités, en contient 10 milliards. Les 2 nombres étant du même ordre de grandeur, cette hiérarchie doit être suffisamment bien construite pour autoriser un concepteur à travailler simultanément sur 3 à 4 niveaux voisins.)

Au début des années 1980, EFCIS, filiale du CEA-LETI travaillant sur ses propres projets (Hanczakowski), se vit proposer le hardware compiler Synopsys. Bien qu’à l’état de prototype, ce produit fut adopté par EFCIS. Cet épisode était révélateur de la raison d’être de l’industrie EDA. Les concepteurs de circuits devant concentrer leurs efforts face à une concurrence mondiale, il leur fallut externaliser cette technologie stratégique, quitte à la racheter ultérieurement. En la mutualisant avec leurs concurrents, ils se prémunissaient contre le risque de la voir disparaître. De plus, en organisant la concurrence au sein même de l’EDA, ils exerçaient une pression sur les prix, ce qui explique que cette niche technologique n’a jamais pesé plus de 1 à 2 % du marché de la microélectronique.

II- Caractéristiques du langage

Ces langages destinés à décrire des circuits électroniques hardware devaient se voir attribuer une sémantique hardware éloignée de celle des langages de programmation dont ils mimaient la syntaxe, mais présentant une sémantique algorithmique. Cette distinction étant, en 1966, encore confuse, elle suscita de nombreuses discussions sur l’usage du langage d’Iverson. S’ajoutait à cela le fait que la syntaxe choisie pour les premiers HDL, dont CASSANDRE fait partie, était de type Algol, donc éloignée d’APL. Néanmoins, certains opérateurs d’APL apportaient une concision et une puissance d’expression du parallélisme qui séduisaient.

En bref, les éléments primitifs de CASSANDRE sont : Unité, Registre, Signal, État.

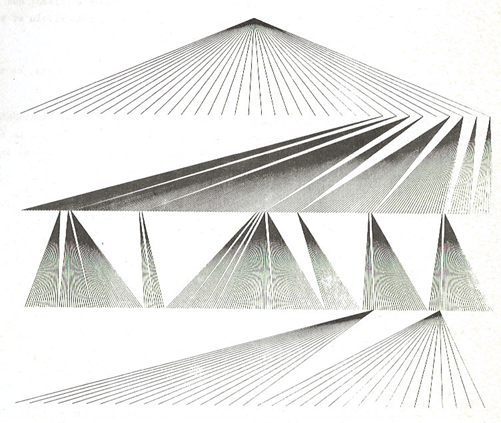

- une Unité représente un module élémentaire du matériel décrit (entité structurelle). Elle peut contenir un réseau d’autres unités interconnectées dont chacune, à son tour, peut contenir un réseau d’unités. C’est donc une notion récursive qui définit une hiérarchie de modèles imbriqués. Les feuilles de cette hiérarchie sont des unités dont les contenus sont entièrement synthétisés. Une telle unité intégrant une importante fonction synthétisée testée et réutilisable dans d’autres conceptions serait aujourd’hui appelée IP.

Exemple de conception hiérarchique

Arbre d’imbrication de toutes les unités du Z0001 (outil David, Ménard)

- un Registre représente un tableau d’éléments de mémorisation. Ce peut être un vecteur, une matrice ou un vecteur de matrices. Chaque élément d’un registre a une sortie de type Signal et 3 entrées : une donnée, une horloge et une condition. Seule l’occurrence d’un signal d’horloge peut changer le contenu d’un registre en lui affectant la valeur de l’entrée donnée.

- un Signal représente une sortie de circuit combinatoire ou de registre. Il dénote les entrées donnée et condition d’un registre, ou l’opérande d’une fonction booléenne dans un circuit combinatoire. Un signal a donc la sémantique d’une connexion, dont la valeur est stabilisée en fin de cycle. Il ne peut être modifié par une horloge en mode synchrone. Toutefois, François Anceau utilisera en mode asynchrone un opérateur de dérivation permettant de fabriquer des horloges locales. Un signal peut être un tableau de dimensions quelconques.

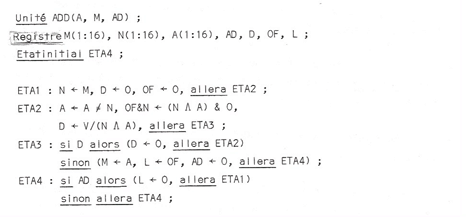

- un Etat désigne « un état non encore encodé ». Chaque unité peut en effet présenter une structure de contrôle locale constituée d’une liste déclarée d’états et de transitions entre ces états, conditionnées ou non par des instructions. Un automate d’états fini contrôle son comportement. Au moment de la synthèse, un codage est créé pour cet ensemble d’états, ainsi qu’un registre pour stocker l’état courant de l’unité. En gardant la liberté d’implémentation du contrôle d’une unité, on se réserve la possibilité de réaliser un contrôle micro-programmé (chaque état devient l’adresse d’un mot d’une mémoire ROM), avec la liste des conditions qui en libèreront l’exécution. Cela ouvre le champ de la microprogrammation, de la compilation de microprogrammes et de l’optimisation des architectures. Ce domaine fut le champ le plus exploité de CASSANDRE dans l’industrie. Voir ci-dessous un exemple simple du style d’une description :

L’unité Z0001, sommet de la hiérarchie produite par le compilateur de circuits logiques Liddell-Fantino

Description en CASSANDRE d’un additionneur parallèle 16 bits

Génération en Algol d’un modèle simulable de l’unité ADD CASSANDRE

III - Développement. Environnement technologique et industriel

Après une période de conception du langage et de prototypage des outils associés, il a semblé souhaitable de confronter les résultats à l’avis d’auteurs américains. L’intention était d’identifier d’éventuels travaux en cours au MIT et à l’Université de Stanford et de rendre visite à Schlaeppi, Iverson, Chu et Breuer, ce que le Professeur Kuntzmann approuva.

Jean Mermet se rendit donc au centre de recherche d’IBM à Yorktown Heights où Hans Schlaeppi, auteur de LOTIS, lui suggéra nombre d’additions relatives au timing des modèles et au séquencement basé sur l’ordonnancement des délais. Il rencontra aussi Kenneth Iverson. Comme tous les chercheurs de Y.H, celui-ci disposait d’une minuscule alvéole de travail, mais aussi d’un 360/91, la plus grosse machine de l’époque, habituellement réservée aux militaires. Il fut enchanté de voir les opérateurs de son langage repris dans CASSANDRE, mais surpris que nous les appliquions à des tableaux en dimension arbitraire, alors qu’il se contentait de vecteurs et de matrices. Lors d’une rencontre ultérieure à Copenhague, Kenneth Iverson nous avoua avoir adopté cette généralisation en APL.

Sur le campus de College Park, Jean Mermet rencontra Y. Chu, qui jugea que CASSANDRE était un bon outil mais trop compliqué pour l’enseignement. Jean Mermet apprécia la simplicité du langage CDL, mais il ne présentait pas d'extension pour traiter des vrais projets industriels. À UCLA, Jean Mermet eut avec M. Breuer une discussion très instructive sur le codage de la partie contrôle des unités CASSANDRE.

D’autres facteurs entrèrent en ligne de compte :

- Le centre scientifique IBM de Grenoble fut créé en 1967 pour mener des travaux avec l'IMAG sur le thème de l'exploitation conversationnelle des ordinateurs. Il fut dirigé jusqu'en 1969 par Jean-Jacques Duby, puis par Max Peltier et Alain Auroux. L’installation de machines IBM 360/67 dans trois universités européennes, Grenoble, Pise et Munich, instaura un environnement technologique privilégié pour l’enseignement et l’ingénierie logicielle. En plus de la productivité accrue des développeurs, grâce au time-sharing et au mode conversationnel, des outils comme le transformateur de grammaires de Griffiths et Peltier apportèrent une aide importante aux chercheurs français dans le développement des modèles CASSANDRE.

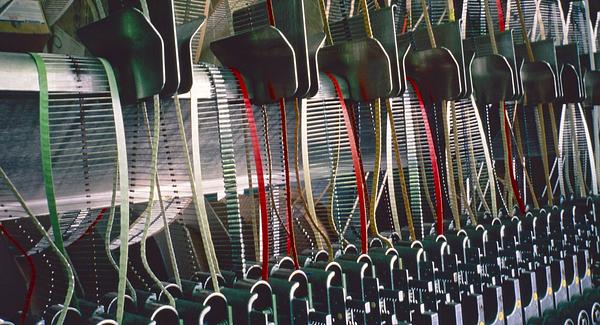

- Un autre facteur d’émulation fut la présence, au sein du centre de recherche du CEA à Grenoble, du LETI, créé et dirigé en 1967 par le Capitaine de Vaisseaux Michel Cordelle. Les équipes placées sous la direction de Jean Kuntzmann avaient des réunions de travail régulières avec l’équipe de conception de circuits de Jacques Lacour (futur directeur de 1983 à 1991), Joseph Borel (plus tard EFCIS puis ST-Micro), Michel Henry... La marine, grâce à Louis Néel, directeur du Centre d’études nucléaires mais aussi Amiral de réserve, avait contre toute attente une grande importance à Grenoble. Jean Mermet fut détaché en tant qu’élève-officier de marine dans l’équipe de Jacques Lacour. Cette affectation lui permit de combler des lacunes dans le domaine de l’électronique, mais aussi de consacrer, avec la bénédiction de son directeur, du temps pour poursuivre les développements de CASSANDRE. L’équipe du LETI servit même de testeur pour ces développements.

- Dans l’industrie, Télémécanique Informatique (TI) se révéla un partenaire de choix. Créé par Guy Jardin en 1962, le département automatisme et électronique de la Société d’électricité Mors avait produit le calculateur industriel MAT 01. Ce département s’installa à Crolles (170 personnes en 1967), puis fut vendu à la société Télémécanique Électrique, dont il devint la division informatique industrielle. Dès le début de CASSANDRE, une coopération s'établit avec Charles Malka, issu lui aussi de l’ENSIMAG. Au fil des ans, 8 personnes de l’équipe CASSANDRE ont rejoint Télémécanique Informatique. Une usine de 14 000 m2 fut créée en 1972 à Echirolles pour héberger 700 personnes, dont 400 ingénieurs et cadres.

Mais l’étatisme bureaucratique, en France, prétend faire mieux que le darwinisme industriel. Les stratèges des french ordinateurs inventèrent « un plan calcul de l’informatique industrielle ». Ils créèrent la SEMS en 1976, au lieu de laisser jouer la concurrence... Le contrat CRI (CASSANDRE et l’industrie) nous donna l’occasion de développer le projet T0001, en collaboration avec C. Malka, comme contre-projet du calculateur T1000. Le but était, en 1970, d’utiliser dans une architecture de mini-ordinateurs les nouveaux circuits MSI, afin d’arriver à un optimum coût-performances et de familiariser l’équipe à la micro-programmation à mots longs.

IV – Commercialisation de CASSANDRE

En mai 1969, le délégué à l’informatique accorda au Professeur Kuntzmann un contrat du CRI pour faire un audit de CASSANDRE chez différents industriels. Ceci nous apporta des relations nouvelles avec plusieurs entreprises.

- La SPERAC, enfant chéri du plan calcul, avait développé un système interne appelé CRISSMASS, que nous devions comparer à CASSANDRE.

- PHILIPS Data Systems initialisa avec Philippe Denoyelle une coopération très appréciée. Les filiales françaises et américaines utilisèrent le simulateur pour la conception de leurs mini-ordinateurs.

- CROUZET devait développer pour la Direction de l’aviation civile le système CAMPANULE (Chaîne Adaptable par Microprogrammation pour Analyse Numérique et Logique). Ils choisirent CASSANDRE pour la mise au point des microprogrammes du projet et firent évoluer l’environnement du système en mettant en évidence les difficultés d’usage.

- TITN (Traitement de l’Information. Techniques Nouvelles) nous proposa de développer un ordinateur micro-programmé. L’Ordoprocesseur fut entièrement décrit en CASSANDRE et simulé. L’élaboration des micro-instructions fit apparaitre le besoin d’un macro-assembleur de micro-programmes.

- IFP (Institut Français du Pétrole). La coopération autour du TETRAMAT comporta : la formation des utilisateurs langage et système (Nov.-Déc. 1970), l’écriture et la simulation des unités logiques élémentaires, le regroupement de ces unités dans une unité globale et sa simulation (Jan.-Mars 1971), suivis de l’écriture des micro-programmes, leur simulation et du feed-back des résultats obtenus (Mai-Juin 1971). La suite et fin de la simulation des microprogrammes s’effectua chez la CEGOS.

Le 15 décembre 1970, le Professeur Jean Kuntzmann décida de créer une équipe de recherche à l’ENSIMAG. L’équipe CASSANDRE, augmentée de C. Le Faou, porteur du programme de simulation électrique IMAG3, en constituait l’essentiel. Ce transfert accompagnait l’idée de constituer entre l’INPG et le CEA un Centre Grenoblois de Logique et d’Informatique pour « l’aide à la conception, la fabrication et l’évaluation des composants et systèmes électroniques ». Ce CEGLI devait avoir un volet industriel (GIE pour la CAO avec la société Matra et le CNET)pour exploiter, entre autres, les logiciels CASSANDRE et IMAG3. Mais au moment de conclure, le GIE annonça qu’il venait de confier la commercialisation d’IMAG3 à la société SESA. Ainsi prit fin, début 1971, la première velléité de créer une société EDA française. Jean Mermet prit alors rendez-vous avec M. Stern de SESA et diverses sociétés pour négocier la diffusion de CASSANDRE. L’affaire fut conclue avec CEGOS, moyennant le versement d’une redevance égale à 25% des revenus. Parmi les sociétés clientes, citons Thomson DIS/SCAS, LTT, Électronique Serge Dassault, Signetics, North American Philips, RTC, TRT, CTI, LEP, Philips Eindhoven et MATRA.

V – CASSANDRE: bénéfices et interrogations

CASSANDRE, ses publications, ses outils associés (universités de Pise, Institut Weismann), et sa clientèle en France, Pays Bas, Angleterre, USA, apportèrent à notre équipe une notoriété qui s’avéra déterminante pour nombre de projets internationaux de l’après CASSANDRE :

Définition de CONLAN : Dominique Borrione présenta à l’International Symposium on Computer Hardware Description Languages and their Applications, New York du 3 au 5 Septembre 1975, une contribution qui favorisa la création d’un groupe pour définir un standard mondial des HDL : CONLAN. Ce groupe, constitué de 4 membres américains et de deux européens (le Pr. Piloty de Darmstadt et D. Borrione), inspira notre projet CASCADE d’intégration en un seul langage d’une famille de dialectes HDL : IMAG3 au niveau électrique, CASSANDRE au niveau RTL, LASCAR au niveau émulation de l’arithmétique et LASSO au niveau système.

Création de VHDL : En 1982, MATRA nous mit en relation avec le département de la Défense américain (DoD) qui s’apprêtait à lancer un appel d’offre pour définir son langage standard pour le projet VHSIC, comme il l’avait fait quelques années plus tôt pour son langage de programmation ADA (J. Ichbiah, CII). Le DoD nous envoya son appel d’offre et nous pensions y répondre, car le projet CASCADE et son équipe associée nous plaçaient en bonne posture. Ce ne fut pas du goût d’IBM qui obtint le classement confidentiel défense trois mois avant le lancement du « call for tender ». Quelques années plus tard, quand le DoD voulut faire de VHDL un standard mondial civil, nous organisâmes l’entrisme européen dans la standardisation IEEE.

VHDL IEEE/1076-1993, comme standard civil : L’avènement de VHDL marqua la fin de CASSANDRE et de ses développements. Cependant, avec la First European Conference on VHDL Methods que nous organisâmes à Marseille en 1990 et celles qui suivirent, la participation européenne à la standardisation de VHDL monta en puissance. De multiples groupes thématiques furent créés en Espagne, UK, Allemagne, Suisse. Ce travail aboutit à des corrections et des changements majeurs du standard, reflétés dans la version 1993, et fut reconnu par les IEEE.

Projets Européens : En 1982, la commission de l’UE décida de financer la recherche sur les systèmes intégrés de CAO de VLSI. Nos relations avec le groupe Philips nous permirent de constituer rapidement un consortium formé des sociétés TMC, RTC, CTI, TRT APT, SGS et du Politecnico di Torino. Le projet CERES (CASCADE Environment for the Realization of Electronic Systems), placé sous notre maîtrise d’œuvre, fut le premier contrat de recherche financé par la CEE. Son budget était de 70M-F pour un total de 180 personnes-années.

Conclusion

Si l’on se penche sur le passé de CASSANDRE, se pose inévitablement la question : « Aurions-nous pu faire mieux ? » Dans le domaine technique, on peut toujours faire mieux. Mais la carrière de CASSANDRE n’a pas été un succès ou un échec à l’aune de sa qualité technique, mais à celle de l’industrie européenne des circuits électroniques. Pourquoi l’Europe a-t-elle su produire un leader mondial en CAD-CAM comme Dassault Systèmes, lequel contrôle aujourd’hui 30% du marché mondial ? Parce que le marché Européen était supérieur à ceux d’Amérique du Nord et d’Asie. Et pourquoi l’Europe n’a-t-elle pas su produire Synopsys, alors que ses créateurs sont européens ? Parce que le marché européen de la micro-électronique a toujours été beaucoup plus petit que le marché américain. La question suivante est donc : « CASSANDRE pouvait-il devenir Verilog à la place de Verilog ? » La réponse, là encore, est négative, mais pour d’autres raisons…

Notes :

pour accéder à la bibliographie complète, se reporter à l'article original sur le site de l'ACONIT.